# **CDMA Crossbar for Network-on-Chip**

Sangeetha G.S<sup>1</sup>, Riyas K. S<sup>2</sup> PG Scholar<sup>1</sup>, Assistant Professor<sup>2</sup> Dept. of Electronics and communication Engg. Rajiv Gandhi Institute of Technology Kottayam, India

Abstract—Network-On-Chip (NoC) is the most scalable interconnection paradigm that is capable of addressing various application needs. In NoCs, data are treated as packets, while processing elements as nodes that are interconnected via routers and switches. As the number of processing elements in a System On a Chip increases the desired performance cannot be achieved by the traditional bus based architecture. As a result packet switching concept (NoC) can be used for the communication between the processing elements. When different processing elements communicate through the same physical link there arise collisions. Collisions are avoided by using Code Division Multiple Access (CDMA) as the medium sharing technique. The basic building block in NoC is a crossbar. Crossbar consists of encoder, adder and a decoder section. Information between the processing elements is transmitted either as ones or zeros. This leads contention. This contention can be eliminated by using compression method. The technique of applying CDMA concept in NoC along with data compression technique is the point to be discussed in this work. The structure of CDMA NoC is proposed and the process is coded and implemented by using Xilinx software in this work.

Index Terms—Network-On-Chip, System on a Chip, Codedivision multiple access (CDMA), Crossbar.

# I. INTRODUCTION

System on a chip known as SoC is an integrated circuit that contains various electronic components such as CPU, GPU, memory, timer etc on a single substrate. SoC uses bus based architecture. Day by day the number of components increases to achieve the desired performance [1]. As a result the components that has to be integrated on a chip also increases which in turn complicate the bus based interconnection. Network On-Chip (NoC) is introduced to reduce the complexity in SoC.

The fundamental building block of NoC is a crossbar. To avoid collisions (When multiple flows require through the same physical link) multiple access technique can be used. The main multiple access technique is Time-Division Multiple Access (TDMA) where the physical link is time shared. The problem with TDMA technique is the bus contention, to avoid this, an alternative Code-division-multiple access is proposed.

In CDMA each user is assigned with unique code [2]. This code is generated by spreading code generator. The spreading code is a binary coding means the code contains only zeros and ones. The encoding and decoding process are used at the transmitter and receiver side respectively. The spreading codes are orthogonal to each other indicating no interference between the encoded data. The advantages of CDMA interconnect include reduced complexity and power consumption, has less wiring complexity than SDMA and less arbitration overhead than TDMA switch.

The basic structure of CDMA NoC consists of encoder, adder and decoder modules. Each processing element is connected to a separate encoder. The data from the PE is encoded with an orthogonal code in the Encoding module.

The coded data from different encoding modules are added together. Then, the sums of data chips are transmitted to receivers. In the receiver, Decoding modules reconstruct original data bits from the sums of data chips.

Much of the previous work has focused on CDMA architecture that result in a complicated router design. In this work CDMA NoC structure along with data compression technique is introduced. The features of this work are

- 1) Introducing CDMA NoC crossbar to increase the processing elements that can be incorporated in a chip

- 2) Applying CDMA concept in NoC

- 3) Applying compression technique to overcome conten-

- 4) Simulation of CDMA NoC using Xilinx

In this work introduction and significance are given in chapter 1 followed by a literature review in chapter 2. The following chapter 3 explains the proposed system architecture. In chapter 4 experimental results obtained is provided. Finally the report is wrapped up with conclusion in chapter 5.

## II. LITERATURE REVIEW

This chapter presents an overview of various approaches used in CDMA NoCs.

X. Wang [1] propose CDMA concept in NoC. CDMA is a channel access method that uses spread spectrum technology. In CDMA each user is assigned with a unique code, generated by a spreading code generator. This code may be Gold code, kasami code, walsh code etc. Codes are orthogonal and have balance properties (number of zeros equal to number of one's).

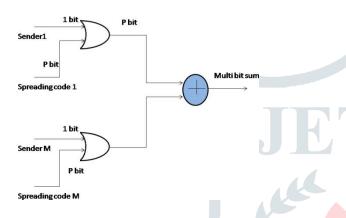

CDMA mainly consists of a transmitter and receiver section [2] [4]. At the transmitter side, data from each user is combined with the spreading code. This operation is known as encoding. The encoded data are then combined together through addition operation. The multi bit sum is used to decode the original data at the receiver side. The process of reconstructing the original data from the multi bit sum is known as the decoding process.

Encoding is usually an XOR operation between the data and spreading code. Consider the spreading code is P bit, and then the message signal is spreaded into P bit by XOR operation. Each bit in a spreading code is called a chip.

Fig. 1. Encoder

Consider that user1 has a message, that is 1 and user2 has message as 0. The spreading codes used for encoding are 0011 and 0100. The encoded data becomes 1100 and 0100 respectively. The addition operation results a sum of 1200. After summation the result is in the form of 0 1 and 2, and can be coded by using binary code. So two bits are sufficient to represent the encoded result.

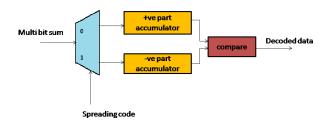

The decoding is usually based on demux- accumulator-compare operation. The multi bit sum is given as the input to the decoder [7]. Based on the chip value of the spreading code the multibit sum are either goes to the +ve part accumulator (if chip value is 0) or -ve part accumulator (if chip value is one). A compare module then compares the accumulator values.

Fig. 2. Decoder

If the +ve part accumulator has larger value than the -ve part accumulator then the decoded data becomes 1, otherwise 0. The disadvantages of the above encoding and decoding process include

- 1) Complexity in design

- 2) Low code utilization

To overcome this standard basis based encoding and decoding process is used. An AND gate is used to encode the data. The result chips are then sent to an accumulator. After the m-chips are accumulated, the accumulator output gives the result. The standard basis also suffers from the following disadvantages [3]

- 1) Long transfer latency

- 2) High power consumption

This leads to a new encoding and decoding scheme know as parallel CODEC technique.

The three steps in parallel CODEC are

- En/De-coder parallelization: use multiple parallel AND gate so that encoding and decoding process will finish in one clock cycle

- Adder parallelization: Addition operation takes place parallel

- Simplification: Parallel encoder ensures that the coded data are always orthogonal. Hence complex modules can be eliminated leads to simplified architecture

Compression technique can be used for reducing contention. An example of compression technique is run length encoding. RLE count the number of occurences of a symbol and replace with only one copy of the symbol along with the count of how many times that symbol occurs. For example AABBBCC is encoded as 2A3B2C. However if there is no repetition of symbols, this method of compression is not useful.

#### III. SYSTEM DESCRIPTION

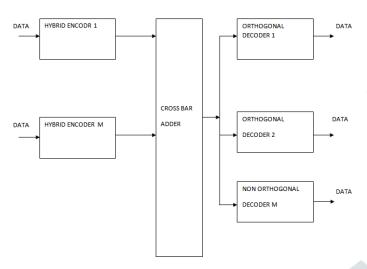

This chapter discusses an overview of CDMA NoC. Block diagram of the proposed system is given in Fig. 3. The basic building block in NoC is basically composed of spreading code generator, hybrid encoder, crossbar adder and a decoder. As the number of processing elements connected to NoC increases, it requires more resources and may create contention problem. Compression technique can be applied in NoC that can reduce the required operations and contention. Basic stages CDMA NoC are given as follows.

#### A. CDMA NoC Crossbar

Spreading code generator: At the transmitter side, the data from different processing elements are encoded using spreading codes. Spreading codes must have orthogonal property. Orthogonal property means that autocorrelation and crosscorrelation value of spreading code are 1 and 0 respectively. CDMA NoC requires the spreading codes that have both orthogonal and balance properties. Different types of spreading codes are walsh code, gold sequence and kasami sequence etc. However, only walshcode has both orthogonal and balance property.

Fig. 3. Block Diagram of the system

Therefore walshcode is chosen as the spreading code for CDMA NoC. Walsh code generator is a combinational circuit.

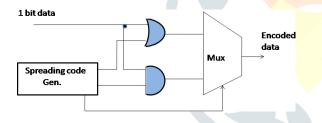

2) Hybrid encoder: Unlike classical CDMA, a hybrid encoder is used, that can encode both orthogonal and non-orthogonal data. The transmitted data bit XORed with walshcode to obtain the orthogonal code and AND operation result in non-orthogonal spread data. A multiplexer is used to choose orthogonal or non-orthogonal inputs.

Fig. 4. Hybrid encoder

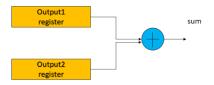

3) Crossbar adder: The encoded output is stored in two registers in accordance with the spreading code. Two registers named as output1 and output2 are used to store the encoded data. If the spreading code value is 0 the encoded data bits is stored in output1 register otherwise stored in output2 register.

Fig. 5. Crossbar adder

Decoders: The function of decoder is to decode the original data from the multibit sum. Since there are two forms of encoded data two types of decoders are used (orthogonal and non-orthogonal decoders)

## B. Compression

Information between the processing elements is transmitted either as ones or zeros. It leads contention. Compressing data will reduce the required operations and decreases the contention. Data compression involves two stages

Fig. 6. Block Diagram of compression technique

- 1) Encoding algorithm: This algorithm takes a message and create a compressed format of the message.

- 2) Decoding algorithm: This algorithm reconstruct the original message from the compressed representation.

Data compression can be divided into two types. Lossless compression and lossycompression. Loss less compression can reconstruct the original message from the compressed representation.

Here we use a compression technique that replaces all consecutive ones that occur five times into zeros. For example if we have a bit stream like 00111 00011 11111, encoding module will divide the bit stream into three sections each section consists of five bits.

If the section contains all bits as one, then the compressed format is all zeros. Any other forms of bit are trans- mitted as such. For the above bit stream compressed format is 00111 00011 00000.

The algorithm use is

- 1) Divide the bit stream into sections.

- 2) Each section consists of five bits.

- 3) If all the bits in a section are ones, replace section with all zeros. Otherwise the section is transmitted as such.

#### IV. RESULTS & ANALYSIS

This chapter discusses about the results of CDMA NoC.

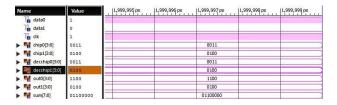

Classical CDMA NoC encoding: Let user1 has a data of 1 and user2 has data as 0.

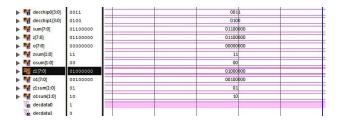

The chip value used for encoding are 0011 and 0100 respectively. The XOR operation will result in encoded data (given as out0 (1100) and out1 (0100)). These encoded data are added to get the sum bit (01100000) as shown in Fig.6 At the receiver side for decoding user1 data we have to use the same spreading code at the transmitter side. The decoding operation finally result in the reconstruction of original data bits (1 and 0 respectively) illustrated in Fig.7

CDMA NoC: Message data to be transmitted is 1. Input to the walsh spreading code generator are given as a1, a2, a3, a4.

Fig. 7. Classical CDMA encoding

Fig. 8. Classical CDMA decoding

n1,n2,n3 indicate counter output. The walsh code for encoding the message data for first clock cycle is 0. Orthogonal output is obtained by the XOR operation between walsh output and message data. Similarly non-orthogonal output is obtained by the AND operation between walsh output and message data. x1 and x2 are temporary registers for storing orthogonal and non-orthogonal outputs. The data bits are transmitted as +1 and -1 voltages indicated in Fig.8

Fig. 9. CDMA NoC

At the decoder side the message data is recovered as shown in Fig.9

Fig. 10. CDMA NoC Decoding

Compression: For compression, we give a 25 bit signal. This bit stream is divided into five sections. Each section contains five bits. If all bits in a section are one (a reference bite $q_1$  becomes 1), then the compress format is all zeros. Otherwise the section is transmitted as such. The given bit stream is decompressed correctly at the receiver side.

Fig. 11. Compression

#### CONCLUSION

In CDMA NoC, the communication channel is overloaded with non-orthogonal codes to increase the channel capacity. The properties of the Walsh spreading code family employed in the classical CDMA crossbar to increase the number of router ports sharing the crossbar without altering the simple accumulator decoder architecture of the conventional CDMA crossbar. Number of processing elements can be increased by using CDMA NoC concept. CDMA NoC consists of spreading code generation, hybrid encoder, crossbar adder and decoders. Walsh spreading code is used for encoding the data. Spreading codes were generated from combinational circuit. The result shows that the decoding operation results in the reconstruction of the original data. Compression technique can be applied in NoC concept, that can reduce the required operations and contention. Crossbars were implemented on Xilinx.

## REFERENCES

- X. Wang, T. Ahonen, and J. Nurmi, "Applying CDMA technique to network-on-chip," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 15, no. 10, pp. 1091-1100, Oct. 2007.

J. Wang, Z. Lu and Y. Li, "A New CDMA Encoding/Decoding Method

- [2] J. Wang, Z. Lu and Y. Li, "A New CDMA Encoding/Decoding Method for on-Chip Communication Network," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 24, no. 4, pp. 1607-1611, Apr. 2016.

- [3] J.Wang, Z. Lu and Y. Li, "A New Parallel CODEC Technique for CDMA NoCs'," IEEE Trans.on Industrial Electronics., vol. 65, pp. 6527-6537, 2018

- [4] K. E. Ahmed and M. M. Farag, "Overloaded CDMA bus topology for MPSoC interconnect," in Proc. Int. Conf. ReConFigurable Comput. FP GAs (ReConFig), Dec. 2014, pp. 1-7.

- [5] K. E. Ahmed and M. M. Farag, "Enhanced overloaded CDMA interconnect (OCI) bus architecture for on-chip communication," in Proc. IEEE 23rd Annu. Symp. High-Perform. Interconnects (HOTI), Aug. 2015, pp. 78-87.

- [6] Z. Qian, P. Bogdan, G. Wei, C.-Y. Tsui, and R. Marculescu, "A trafficaware adaptive routing algorithm on a highly reconfigurable network-onchip architecture," in Proc. 8th IEEE/ACM/IFIP Int. Conf. Hardw./Softw. Codesign, Syst. Synth., New York, NY, USA, Oct. 2012, pp. 161-170.

- [7] S. Kumar et al., "A network on chip architecture and design methodology," in Proc. IEEE Comput. Soc. Annu. Symp. (VLSI), Apr. 2002, pp. 105-112.

- [8] B. Halak, T. Ma, and X. Wei, "A dynamic CDMA network for multicore systems," Microelectron. J., vol. 45, no. 4, pp. 424-434, Apr. 2014.

- [9] Yiqun Wang, Yongpan Liu and Shuangchen L, "PacC: A Parallel Compare and Compress Codec for Area Reduction in Nonvolatile Processors", IEEE Trans. on Very Large Scale Integr. (VLSI) Syst., vol. 22, no. 7, July 2017

- [10] D. Huffman, A method for the construction of minimum-redundancy codes, Proc. IRE, vol. 40, no. 9, pp. 10981101, Sep. 1952.

- [11] R. Williams, An extremely fast Ziv-Lempel data compression algorithm, in Proc. DCC, Apr. 1991, pp. 362371.

- [12] J. Trein, A. Schwarzbacher, B. Hoppe, and K. Noff, A hardware implementation of a run length encoding compression algorithm with parallel inputs, in Proc. ISSC, Jun. 2008, pp. 337342.